### **Sensors & Transducers**

© 2013 by IFSA http://www.sensorsportal.com

# The Design of Multi-channel Signals Source with High-speed and High-precision Based on FPGA

<sup>1</sup> Xiao-Dan DU, <sup>2</sup> Qing HU, <sup>1,3</sup> Tao YAN, <sup>1,3</sup> Yong-Hong LIU

<sup>1</sup>College of Information Science & Technology of Chengdu University,

Sichuan, Chengdu, 610106, China

<sup>2</sup>College of Electronic and Information Engineering of Chengdu University,

Sichuan, Chengdu, 610106, China

<sup>3</sup>Key Laboratory in Colleges for Pattern Recognition and Intelligent Information Processing

of Sichuan Province, Sichuan, Chengdu, 610106, China

<sup>1</sup>E-mail: xiaodandu@yeah.net

Received: 26 March 2013 /Accepted: 14 May 2013 /Published: 30 May 2013

**Abstract:** The multi-channel signals source that the structure is simple and flexible control is proposed in the article, with FPGA and high-speed D/A as its core. The choice of parts of apparatus, hardware constitution and design of software of the signals source are recommended here. Before the hardware designed, detailed theoretical analyses and quantitative description for the key factors on effecting the precision of signal source are given, and when debugging in hardware circuit is completed, on the base of analysis, errors estimation were verified with experimental results. It has provided high-precision signal related to the static and dynamic characteristics test accuracy of measured system for encoder and memory. By experiment and application it can meet the system requirements and has some theoretic and practical value. *Copyright* © 2013 IFSA.

**Keywords:** Multi-channel, Signals source, FPGA, High-speed, High-precision.

### 1. Introduction

There are more requirements to the output amplitude accuracy of the source signal, to the frequency accuracy and stability, to the number outputs and controllability of signals in modern electronic measurement. So we must design a signals source with producing large amounts of the standard signal and guarantee the high accuracy, high stability, maneuverability and operability of signals. The signals, with continuous phase transformation and frequency stability, can be controlled real-time in frequency, phase and amplitude.

The traditional signals source is an independent source, depending on hardware mainly, without

computer participating in. It has complex hardware design and hasn't played software functional fully. In the system, the signals source is programmed by software. By that, these Standard signals' waveform are quantified and the quantitative data are preset in memory. The Communications between the system and computer rely on USB2.0.

## 2. Analysis of Accuracy of the Signals Source

Provided high-precision signals, it related to the static and dynamic characteristics test accuracy of measured system. Generally, the factors that affect

164 Article number P SI 360

the accuracy of the sources are in the following mainly: a variety of circuit noise, static and dynamic parameters of DA converter, Operational Amplifier's zero-drift and static and dynamic accuracy, resistance deviation and resistance drift in resistor network, shut-off and conduction delay of electronic switch, no synchronization between electronic switch and DA conversion and so on.

### 2.1. The Electronic Switch's Effect in Accuracy

Signal output accuracy is required to reach 0.01 % in the system. So signal amplitude of capacitance C in a channel after t1charging should be greater than full range of 99.99 %.And in other channel switching process, the leakage voltage in the channel after t2 discharging should be less than full range of 0.01 %.

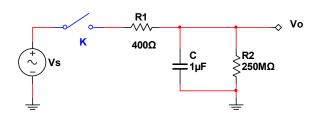

In the design we use ADG506 as electronic switch. It's contact resistance is about  $400~\Omega$  in the working and is more than 1kM in the else. We can Use the capacitance for polypropylene capacitor, their leakage resistance is greater than 1 kM. LM324, the input impedance is greater than 250 M, is adopted as Operational amplifier in the design. Therefore, the whole leakage resistance of the total device is about 250 M. The equivalent circuit is shown Fig. 1.

Fig. 1. The equivalent circuit.

From the Fig. 1, we can know that capacitance C can be charged through  $R_1$  when the switch is turn-on; otherwise, capacitance C will discharge through Leakage resistance  $R_2$ . The charging process is:

$$U_{O} = (U_{S} - U_{O}^{'})(I - e^{-\frac{t_{I}}{\tau_{I}}}) + U_{O}^{'}, \tag{1}$$

When Corrugated coefficient is 1‰, there is  $1-e^{-\frac{t_1}{r_1}} \ge 0.999$ . In ADG506, Not synchronized and the switching delay time should be less than 400ns. So  $t_S \approx 0.4 \, \mu s$ , Then there is:

$$C \ge \frac{-4\,\mu s}{R_1 \times \ln 0.001} = \frac{-4\,\mu s}{400 \times 6.9} = 1449\,pF$$

and

$$C \ge \frac{-64 \times 4 \,\mu s}{R_2 \times ln \, 0.999} = \frac{-256 \,\mu s}{10^{13} \times ln \, 0.999} = 2.56 \, pF$$

To meet the design requirements, we choose 102 capacitance.

### 2.2. The PCB's Effect in Accuracy

Crosstalk is a Noise voltage signal that is brought owing to electromagnetic coupling between adjacent signals line, namely, the energy is coupled by a line to another line. To the higher signal accuracy system, crosstalk noise can further reduce signal quality and margin to other transmission line, taking into account accuracy, this paper focuses on the peak output voltage of crosstalk noise.

$$V_{FE} = \frac{1}{2} L_S (Z_0 C_m - \frac{L_m}{Z_0}) \frac{dv_s}{dt}$$

(2)

$$V_{NE} = K_{EN} \upsilon_0 \tag{3}$$

Young-Soo Sohn has brought out experience formula of  $C_S$ ,  $L_S$ ,  $C_m$  and  $L_m$  and approximate impedance formula of single line in PCB. As follows formula (4), (5), (6), (7), (8).

$$\frac{C_t}{\varepsilon} = [1.15(\frac{W}{H})^{0.963} + 1.07(\frac{T}{H})^{0.049}] + exp(-3.52\frac{S}{H})[0.75(\frac{W}{H})^{0.25} + 2.7(\frac{T}{H})^{1.34}],$$

(4)

$$\frac{C_m}{\varepsilon} = 1.17 \left(\frac{W}{H}\right)^{0.083} \left(\frac{S}{H} + 0.402\right)^{-0.78} + \left(\frac{S}{H} + 1.32\right)^{-0.8} \left[ -1.36 \left(\frac{W}{H}\right)^{0.037} + 0.227 \left(\frac{T}{H}\right)^{0.98} \right],\tag{5}$$

$$\frac{L_s}{\mu_0} = 3.71 (\frac{H}{W})^{0.04I} + 0.018 (\frac{H}{W})^{-0.73} - 3.39 (\frac{H}{T})^{-0.0006} + exp(-1.89 \frac{S}{H}) [0.75 (\frac{H}{W})^{-0.0052} - 0.84 (\frac{H}{T})^{-0.0026}],$$

(6)

$$\frac{L_m}{\mu_0} = \left[ -0.415 \left( \frac{H}{W} \right)^{-0.16} - 2.38 \left( \frac{T}{W} \right)^{1.18} \right] + \left( \frac{S}{H} + 1.07 \right)^{-2.6} + \left( \frac{S}{H} + 0.89 \right)^{-2.03} \left[ 0.418 \left( \frac{H}{W} \right)^{0.13} + 1.37 \left( \frac{T}{W} \right)^{1.09} \right], \tag{7}$$

$$Z_0 = \sqrt{L_s / C_t} \tag{8}$$

Therefore, from the formula (4), (5), (6), (7), (8), we can see distal crosstalk interference will be eliminated when  $Z_0C_m - L_m/Z_0 = 0$  and  $Z_0 = \sqrt{L_s/C_t}$  or  $L_m/C_m = L_s/C_t$ . So we are not layout line between the pin of integrated chip in the PCB and should add earth wire or use wide wire around in easy interference parts. Do not forms a loop in any signal, if inevitable, must be allowed to loop area as small as possible. To improve anti-interference ability of the system we use 4 layer boards in PCB in the design.

#### 2.3. The DA Effect in Accuracy

Based on high-precision, we must select a high-resolution, high-precision D/A Converter in the design. As is known to all, D/A converter the analog output rely ultimately on voltage reference source Predictably, voltage references of the output voltage is directly influence to the precision and stability.

We use A/D768AR, a high-speed 16-bit digital-to-analog converter, as AD In the system. The AD768 may be used in either current-output mode with the output connected to a virtual ground, or voltage-output mode with the output connected to a resistive load.

In current output mode:

$$I_{out} = (DACCODE / 65536) \times (I_{REFIN} \times 4), \qquad (9)$$

In voltage output mode:

$$V_{out} = I_{out} \times R_{LOAD} // R_{LAD}, \qquad (10)$$

$I_{REFIN}$  is the current applied at the  $I_{REFIN}$  pin, determined by  $V_{REF}$  /  $R_{REF}$ . Substituting for  $I_{out}$  and  $I_{REFIN}$ ,

$$V_{out} = -V_{REF} \times (DACCODE/65536) \times 4 \times [(R_{LOAD}//R_{LAD})/R_{REF}]$$

(11)

For application flexibility and multiplying capabilities, the reference amplifier is design to offer adjustable bandwidth that can be reduced by

connecting an external capacitor from the NR node to the negative supply pin,  $V_{EE}$ . This capacitor lim it's the bandwidth and acts as a filter to reduce the noise contribution from the reference amplifier. The voltage output is then a function of the ratio of  $(R_{LOAD}/\!/R_{LAD})/R_{REF}$ , allowing for cancellation of resistor drift by selection of resistors with matched characteristics.

### 3. The Programmer of System and Hardware Constitution

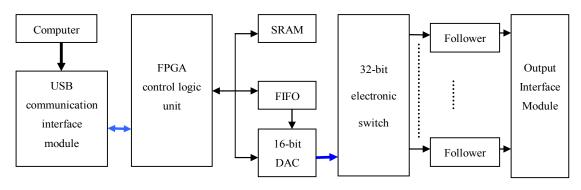

This system has put forward a new method of signal source realization. Using the principle of DDS, computer technology is been into the signal source implementations Through the USB bus. The hardware design will be softened using the power of computer. FPGA is used as center logic control. Hardware circuit principle diagram Fig. 2.

The basic principle for the signal source: Computers send forth Commands and waveform number to FPGA by the USB interface module. Then the FPGA receive computer orders and accomplish the following two tasks according to different command. The first, in the controlling of FPGA the waveforms are read form FIFO and are stored to SRAM. The second is to control the waveform read an SRAM data to the D/A converter, and control the D/A converter finishes conversion.

In the D/A conversion process, the advancement of the memory address pointer should be synchronized with the multi-switch forward address pointer. AD824 is chosen in the design, the AD824 is a quad, FET input, single supply amplifier, featuring rail-to-rail outputs. Its slew rate is  $2V/\mu s$ , the ability of the output to swing rail-to-rail enables designs to build multistage filters in single supply systems and maintain high signal-to-noise ratios. When peak-to-peak value occurs in adjacent two channels signal to overact next channel stable output demands  $(8V/2V)/\mu s = 4\mu s$ , so electronic switch must be opened after  $4\mu s$  in the D/A conversion ending, otherwise channel interference will arise.

Fig. 2. Source hardware principle diagram.

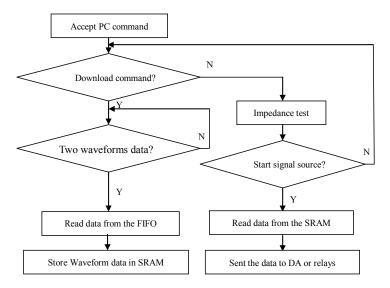

# 4. The Design of Logical Control Unit in FPGA

As the center logic control devices of the signal source, FPGA has the following functions: to analyze Communication Protocol between the system and PC; to control storage and read of waveform data; to control DA conversion and electronic switch address propulsion; to control signal generator; to control impedance test and so on. The program control flow chart is as shown in Fig. 3.

Limited by the USB data transfer, each received 18 valid data which is truly effective data bits  $D_7 \sim D_0$ . Because there are 16 bit waveforms data in the

signals source, the device must receive two effective data to synthesize a 16-bit waveform data which is sent in accordance with the first low 8 bits, then the high order 8 bits. The PC issue data in accordance with the address-Command-Data. So, when the system is working, to determine whether the received address matches the address for the system, if it is, then to judge the specific order form of the second 18-bit data. If the data are download command flag, to set write signal of FIFO is valid, the valid data has been received at this time is the waveform data. And, a 16-bit waveform data, integrating the before low 8-bit data and the after low 8-bit data, will be written into FIFO.

Fig. 3. Program flow chart of FPGA.

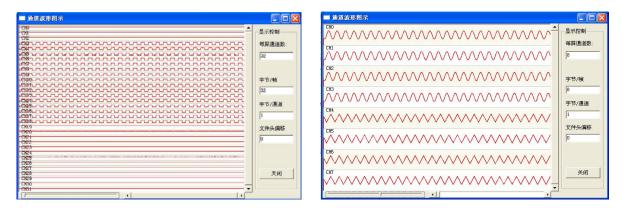

Fig. 4. Self-test wave of signal source.

#### 5. Conclusion

The system has been put into use, and is involved in some large test. In the experimental process, it has provided high-precision signal for encoder and memory. It provides the basis for developing high-accuracy encoder and memory. Fig. 4 is self-test wave of signal source; we can be seen the design can conform to the system requirements.

### Acknowledgements

Fund Project: 1. Scientific Instrument Shared System of Southwest. The project is supported by Educational Department of China. 2. Research and Application of QoS Real-time Video Stream (NO.09ZB114). 3. Research on the Key Technology of Intelligent Campus Network Construction Based

on the Internet of Things. The project is supported By Educational Department of China (NO.11ZB278).

#### References

- [1]. Young-Soo Sohn, Jeong-Cheol Lee, Hong-June Park, et al., Empirical Equations on Electrical Parameters of Couple Microstrip Line for Crosstalk Estimation in Printed Circuit Board, *IEEE Transactions on Advanced Packaging*, Vol. 24, Issue 4, 2001, pp. 521-527.

- [2]. Cheng Gao, Wei Guo, Jiaoying Huang, Single-Event-Upset (SEU) Mitigation Techniques for Routing Resources of SRAM-FPGA, *IJACT*, Vol. 4, Issue 20, 2012, pp. 205-213.

- [3]. Chao Huang, Li-Xiang Ren, Er-Ke Mao, A systematic frequency planning method in Direct Digital Synthesizer (DDS) design, *IEEE Wireless Communications & Signal Processing*, 2009, pp. 1-4.

- [4]. Yuzhong Li, Research and Design on a Novel Optoelectronic Current Transformer Based on FPGA and DSP, JDCTA, Vol. 6, Issue 7, 2012, pp. 206-215.

- [5]. Zhou Libo, Bai Na, Research of High-speed Image and Number's Recognition System Based on FPGA, JDCTA, Vol. 6, Issue 19, 2012, pp. 239-245.

- [6]. T. Nandha Kumar, Haider A. F, Almurib, New Chin-Ee, Fine grain faults diagnosis of FPGA interconnect, *Microprocessors and Microsystems*, Vol. 37, Issue 1, 2013, pp. 33-40.

- [7]. Vinay B. Y. Kumar, Siddharth Joshi, Sachin B. Patkar, H. Narayanan, FPGA Based High Performance Double-Precision Matrix Multiplication,

- International Journal of Parallel Programming, Vol. 38, Issue 3, 2010, pp. 322-338.

- [8]. Qinglin Zhang, Shuzhen Chen, Yijun Luo, Shan Wang, High-speed parallel matched filter designing and FPGA implementation, Wuhan University Journal of Natural Sciences, Vol. 15, Issue 4, 2010, pp. 335-339.

- [9]. Meher P. K., Chandrasekaran S., Amira A., FPGA Realization of FIR Filters by Efficient and Flexible Systolization Using Distributed Arithmetic, *IEEE Transactions on Signal Processing*, Vol. 56, Issue 7, 2008, pp. 3009-3017.

- [10]. Jia Hui-Juan, Research on the Technology of RS485 over Ethernet, *The International Conference on E-Product, E-Service and E-Entertainment (ICEEE' 2010)*, 2010, pp. 1-3.

- [11]. NI Haiyan, HU Chao, MA Changwang, Research on a 485-serial network architecture in intelligent uptown management, 2006 IEEE Conf on Mechatronics and Automation. Luoyang: IEEE Press, 2006, pp. 400-405.

- [12]. Shihong Qin, Design of the Multi-computer communication system based on RS485, 2011 International Conference on Electric Information and Control Engineering (ICEICE), 2011, pp. 1318-1320.

- [13]. Gao Zhen-Bin, FPGA implementation of a multichannel HDLC protocol transceiver, 2005 International Conference on Communications, Circuits and Systems, 2005, pp. 1200-1203.

- [14]. Bin Huang, Design of a multi-channel high speed FIFO applied to HDLC processor based on PCI bus, *IEEE* 2002 International Conference on Communications, Circuits and Systems and West Sino Expositions, 2002, pp. 1476-1480.

2013 Copyright ©, International Frequency Sensor Association (IFSA). All rights reserved. (http://www.sensorsportal.com)

International Frequency Sensor Association (IFSA) Publishing

### **Digital Sensors and Sensor Systems: Practical Design**

Sergey Y. Yurish

Formats: printable pdf (Acrobat) and print (hardcover), 419 pages

ISBN: 978-84-616-0652-8, e-ISBN: 978-84-615-6957-1 The goal of this book is to help the practicians achieve the best metrological and technical performances of digital sensors and sensor systems at low cost, and significantly to reduce time-to-market. It should be also useful for students, lectures and professors to provide a solid background of the novel concepts and design approach.

#### Book features include:

- Each of chapter can be used independently and contains its own detailed list of references

- Easy-to-repeat experiments

- Practical orientation

- Dozens examples of various complete sensors and sensor systems for physical and chemical, electrical and non-electrical values

- Detailed description of technology driven and coming alternative to the ADC a frequency (time)-to-digital conversion

Digital Sensors and Sensor Systems: Practical Design will greatly benefit undergraduate and at PhD students, engineers, scientists and researchers in both industry and academia. It is especially suited as a reference guide for practicians, working for Original Equipment Manufacturers (OEM) electronics market (electronics/hardware), sensor industry, and using commercial-off-the-shelf components

http://sensorsportal.com/HTML/BOOKSTORE/Digital\_Sensors.htm